Intel Quad-Core et Apple

Avec le Core 2 Quad-Core QX6700 présenté vendredi, Intel a rattrapé son retard sur ses concurrents. Doit-on y voir l’une des conséquences inattendues du partenariat avec Apple?

A ce propos si l’on m’avait prédit il y a 2 ans qu’Intel France prendrait la peine d’envoyer à certains membres de La Rédac des données sous embargo de leur prochain processeur… et que pour ma part j’irais les consulter pour en faire un article !

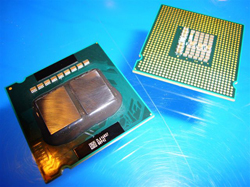

Intel Core 2 Extreme QX6700 Quad-Core : 2×2=1

Le fondeur de Santa Clara étant désormais le fournisseur attitré de Cupertino, celui-ci n’ayant jusqu’ici qu’à s’en féliciter (voir la chronique du 1er novembre), voici donc sans prétention aucune les grandes lignes de de qu’on peut retenir de la nouvelle puce :

Tout d’abord, il ne s’agit pas véritablement d’une puce quadri-core à proprement parler, mais d’une paire de processeurs Dual Core, en l’occurrence 2 unités Core 2 Duo placées sur 2 socles différents même si les 4 cores partagent le même socket et fonctionnent indépendamment les uns des autres. Intel a argumenté cette astuce pour des raisons de rapidité de développement, de rationalisation de production et d’encombrement des socles. L’arrivée d’AMD dans 9 mois avec le K8L et ses 4 noyaux véritablement indépendants devrait permettre de se rendre compte dans quelle mesure ce discours était sincère(Quad-Core Processing).

Le QX6700 est constitué de 582 millions de transistors gravés en 65 nanomètres et donc répartis sur 4 noyaux indépendants regroupés 2 à 2, avec 8 Mo de cache L2 et un bus frontal de 1066 MHz. Dans un premier temps, le Quad-Core Extreme sera livré pour une vitesse d’horloge de 2,67 GHz.

Le rendement de chaque cycle est donné par le constructeur comme amélioré sur la vitesse d’exécution et le multithreading, avec désormais jusqu’à 4 instructions complètes traitées par cycle d’horloge, codées sur 64 bit (Wide Dynamic Execution). Un nouveau système d’accès mémoire baptisé Smart Memory Access optimise l’utilisation de la bande-passante, avec un nouveau mécanisme de prédiction destiné à réduire le temps d’attente des instruction à la volée. De nouveaux algorithmes déplacent les données de la mémoire système vers la mémoire cache en prévision de leur exécution, afin de garder le pipe-line toujours alimenté et d’éviter les temps morts dans le traitements des instructions. La mémoire cache L2 est allouée à chaque noyau dynamiquement sur la base de sa charge de travail, afin de réduire au maximum le temps d’accès aux données les plus fréquemment utilisées par ceux-ci (Advanced Smart Cache).

Les calculs vectoriels et ceux en virgule flottante bénéficient des améliorations apportées au jeu d’instructions SSE, pour un certain nombre d’applications professionnelles d’encodage audio ou video, ou de calcul scientifique. Les instructions 128 bit sont désormais délivrées sur la base d’un débit de 1 par cycle d’horloge, ce qui double la vitesse d’exécution effective par rapport aux générations précédentes de Santa Clara (Advanced Digital Media Boost).

La technologie de virtualisation des plate-formes a fait un temps couler beaucoup d’encre, au point que certains ont pu y voir un peu hâtivement l’une des raisons du passage d’Apple avc armes et bagages chez Intel : on oublie trop souvent que celle-ci était depuis un bon moment à l’ordre du jour chez tous les fabricants de puces pour serveurs, IBM et AMD y compris [[Il y a d’ailleurs fort à parier que c’est en définitive à la solution d’IBM que le brevet d’Apple sur le sujet qui a tant électrisé le web faisait référence…]] Quoi qu’il en soit, celle-ci est présente sur la puce, autorisant plusieurs systèmes à tourner sur une même machine sur des plate-fformes virtuelles, l’activité de chacune étant isolées dans une partition (Intel VT).

Outre une nouvelle sonde thermique numérique (DTS) placé sur chaque socle, un connecteur à 4 broches est prévu, pour le contrôle précis de la température réelle de la puce, en adaptant au plus juste la vitesse de fonctionnement du ventilateur, ceci dans le but avoué de réduire la nuisance sonore produite par celui-ci (Intel Designed Thermal Solution for Boxed Processors).

Enfin – mais est-il besoin de le rappeler? – le nouvel Intel Core 2 Extreme QX6700 Quad-Core fonctionne sur le mode d’adressage 64 bit comme ses prédécesseurs de la famille Core Duo 2, ce qui lui permet notamment d’utiliser des quantités supplémentaires de mémoire vive, et de traiter ainsi de “paquets” plus importants… pour peu que l’OS et l’application sachent en tirer parti !—–

Un air de déjà vu?

Rappelons tout d’abord que tous les fabricants de puces sont confrontés à la même gageure : le recours utilisé à des finesses de gravure de plus en plus considérables, pour contrebalancer la chaleur produite par l’accumulation des centaines de millions de transistors qui composent les puces modernes, se heurte au comportement aléatoire des électrons à présent que l’on travaille à l’échelle de la matière.

Les fondeurs ont d’ailleurs dû commencer de se préoccuper de ce problème dès 2002-2003, lorsqu’ils ont atteint les alentours de 0,13 microns (130 nanomètres), et l’on en est arrivé à des finesses de 0,06 microns (65 nanomètres) sur l’actuelle génération de Core Duo et Core Duo 2 qui équipe désormais la totalité de l’offre d’Apple… en attendant les 45 nanomètres.

On touche ici aux difficultés auxquelles La Pomme a du faire face avec ses fournisseurs de puces successifs… et auxquels elle a répondu en passant de l’un à l’autre : peu de chauffe et une dissipation thermique raisonnable, avec pour finir une impossibilité d’obtenir une montée en fréquence synonyme de gain de puissance, chez Motorola ; un gain de puissance obtenu par IBM en grande partie grâce à l’adoption de la technologie des mots informatiques longs (VLIW) qui code les requêtes sur 64 bits, et à la gravure sur 90 nanomètres. Las ! faute d’investissements en R&D suffisants, ce fut au prix d’une débauche thermique, au point que les derniers modèles du PowerPC 970 ont du être refroidis par watercooling… On l’a vu avec les dernières machines sorties par Apple : Intel semble – pour l’instant – avoir trouvé la bonne formule avec sa technologie de microarchitecture NetBurst, en tous cas celle qui a enfin permis à Apple de faire enfin grimper en puissance ses ordinateurs portables, sur ce qui est devenu la tendance porteuse du marché informatique depuis 2 ans (voir la chronique du 1er novembre).

A un peu plus de 2 ans d’intervalle, il est assez amusant de noter que les principaux points mis en avant par le communiqué de presse d’Intel – multicore optimisé par le cache L2, optimisation des cycles processeur et de la température, unité de calcul vectoriel et calcul sur 64 bits sont pratiquement ceux du PPC 970 MP, le premier premier Dual Core d’IBM, qui avaient fort opportunément “fuité” chez ThinkSecret au moment où les difficultés de Big Blue ont commencé à devenir perceptibles (voir la chronique du 25 juillet 2004). C’est cette dernière version de PowerPC 970 fabriquée pour Apple qui allait équiper l’ultime génération de PowerMac G5 en octobre 2005, avec notamment un Dual Dual Core…

Avec 4 instructions codées sur 64 bit par cycle, le Core Duo 2 rejoint l’un des principaux avantages du PowerPC RISC. Avec une instruction SIMD par cycle sur 128 bits, l’unité SSE se rapproche de l’AltiVec, même si celui-ci continue de différer par bien des aspects. On se souvient peu qu’en tant que co-fondateur du consortium PowerPC en 1991, au même titre que Motorola et IBM, Apple a travaillé avec un certain nombre d’ingénieurs à la conception et l’évolution des différentes versions de PowerPC qu’elle a utilisée. Keith Diefendorff qui a chapeauté pour Apple le développement de l’AltiVec – dont Apple était le principal utilisateur – avait, avant de jeter les bases du processeur RISC, été un familier de la plate-forme x86, d’abord chez Motorola, puis chez AMD, après que celui-ci ait racheté NexGen… Apple a-t-elle une nouvelle fois aiguillé les recherches de son fondeur attitré, en fonction de ses propres besoins?

On sait en effet que parmi les clients potentiels de la nouvelle puce “extreme”, se trouvent au premier chef les scientifiques et les professionnels de l’image et du son… chez qui Apple recrute en grande partie sa clientèle professionnelle !

On comprendrait mieux dès lors ce que Pat Gelsinger ou Eric Kim (voir la dépêche du 3 octobre), tous les deux Vice-Présidents d’Intel, pouvaient avoir en tête lorsqu’ils se félicitaient, à quelques jours d’intervalle, du partenariat conclu avec Cupertino. Pat Gelsinger glissait même qu’un certain nombre de projets étaient toujours sous le boisseau avec Apple, maintenant que la transition de la gamme vers Intel est achevée.

Est-il pour autant urgent de se lamenter, en attendant impatiemment et la carte bleue fébrile, qu’Apple intègre la nouvelle puce dans l’une ou l’autre de ses lignes de MacPro ou d’Xserve ? Les choix technologiques d’Intel montrent qu’à Santa Clara, on a préféré privilégier une transition en douceur – y compris au niveau des cartes-mères qui restent les mêmes – à une rupture franche comme s’y prépare AMD, programmée dans 6 mois maintenant. C’est que – comme l’ont montré les excellentes évaluations menées sur la nouvelle puce par Hardware.fr et Matbe.com, la plupart de applications ne savent pas encore tirer parti du multithreading et de la répartition de la charge telle que l’autorise le Quad-Core QX6700… Du moins sur PC ?

D’ici janvier 2007, date à laquelle la technologie Quad-Core est prévue pour intégrer l’ensemble des segments, Apple aura sans doute mis à profit l’année d’avance dont elle dispose dans l’expérience de la technologie Quadri Core pour faire avancer l’ensemble de son offre logicielle…